aulaDS002 - eletronica24h

Menu principal:

aulaDS002

Educacional > Cursos > Digital Sequencial

ELETRÔNICA DIGITAL - CIRCUITOS SEQUENCIAIS

Aula 02: FLIP FLOP JK - FLIP FLOP D - FLIP FLOP T

1 O Flip Flop Tipo JK

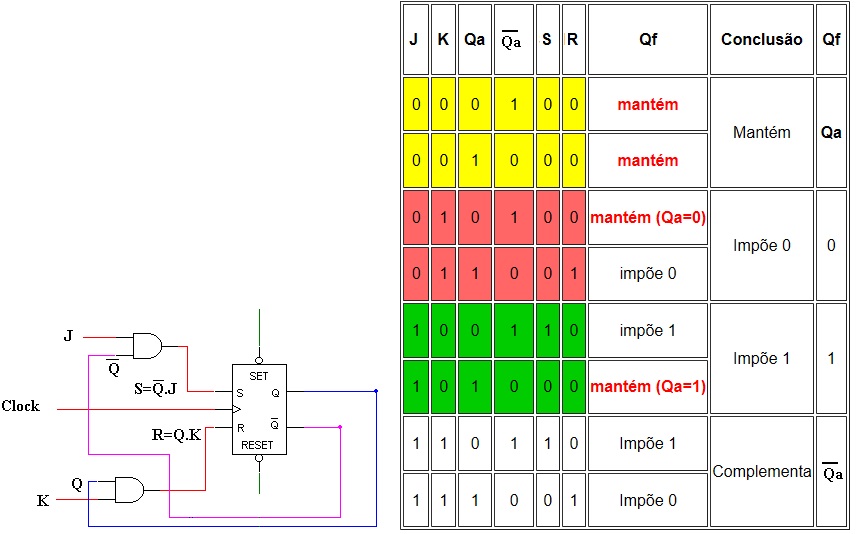

É obtido usando um FF RS com realimentação como mostrado na Figura 1.

( a ) ( b )

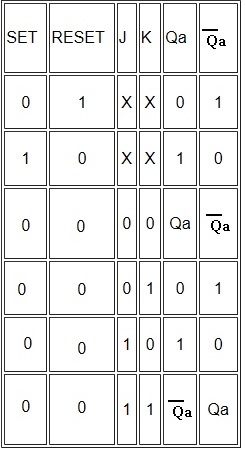

Figura 1 - ( a ) FFJK obtido a partir do RS ( b ) Tabela Verdade

Arquivo Multisim Live

Atenção que, para J=K=1 para obter a ultima linha da TV é necessário que os atrasos das portas sejam convenientes,caso contrário pode haver oscilação das saídas. O problema é totalmente resolvido com o FF JK mestre escravo.

2 O Flip Flop Tipo JK Mestre Escravo

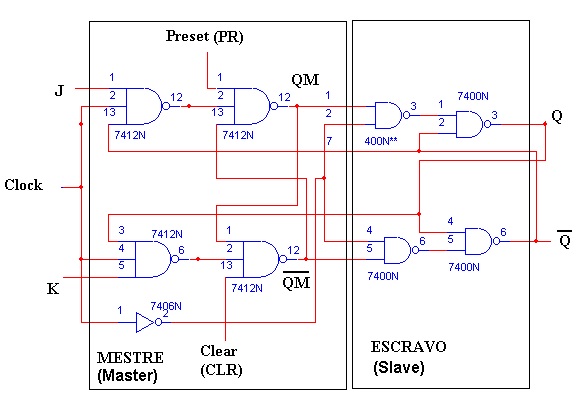

Esse FF elimina a indeterminação da ultima linha da TV do FF RS. É construído a partir de dois FF RS um chamado de mestre (Master) e outro de escravo (Slave). A Figura 2 a seguir mostra a sua construção.

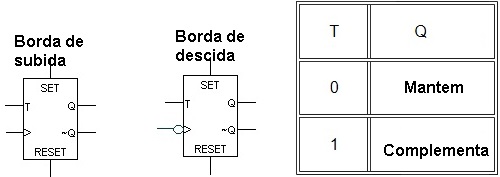

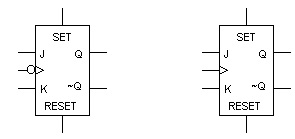

Observem que, quando o Clock=1 o FF mestre estará habilitado e portanto o que estiver na sua entrada passará para a sua saída (QM) de acordo com a TV de um FF JK, enquanto isso o FF escravo estará desabilitado pois o seu Clock=0. Quando o clock passar para 0, o conteúdo das entradas do escravo passará para a saída Q. Como a saída só mudará quando o clock passar de 0 para 1 dizemos que este tipo de FF é sensível à borda de descida. A Figura 3 mostra o símbolo dos FF sensível à borda de descida e subida. O simbolo para essas condições é a pequena bolinha junto ao triangulo. Com bolinha é sensivel a borda de descida, sem a bolinha a mudança acontece na subida do clock.

( a ) ( b )

Figura 3 - ( a ) FF JK sensível à borda de descida ( b ) FF JK sensível à borda de subida

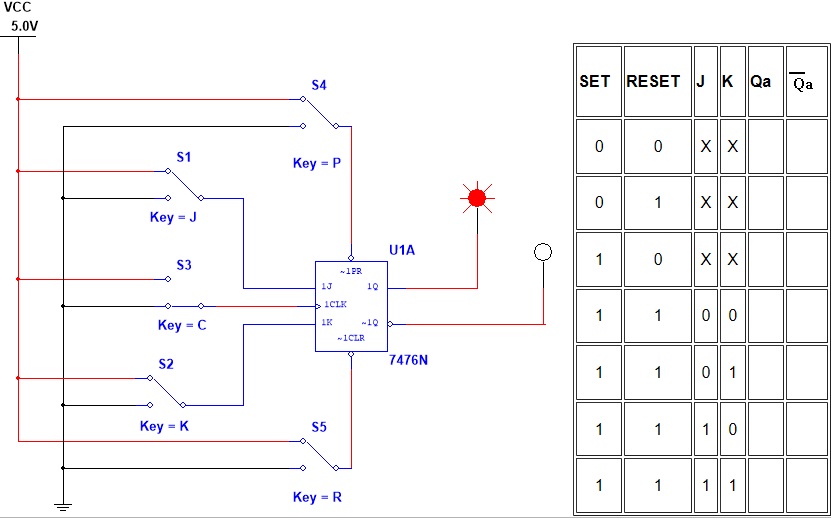

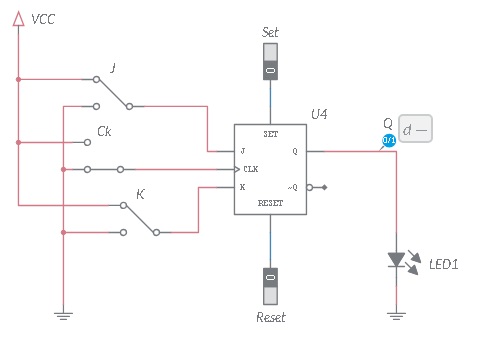

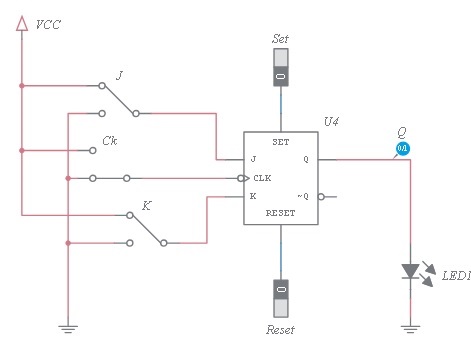

Obs: A entrada de Set muitas vezes é chamada de Preset e a de Reset de Clear são usadas para impor um determinado estado 0 ou 1. A Tabela Verdade daq Figura 4 mostra como devem ser usadas.Observe que, independentemente das entradas J e K (X na tabela verdade) a saida Q será imposta em função dos valores de S e R. Por exemplo, S=1 e R=0 impõe 1 na saida, e S=0 e R=1 impõe zero na saida.Figura 4 - Tabela Verdade do FF JK mestre escravo com as entradas de preset (set) e reset (clear).Observar que para funcionamento normal as entradas assíncronas (SET e RESET) devem estar em nível alto. (SET=RESET=1)Para impor 1 de forma assíncrona deveremos ter SET=1 e RESET=0.Para impor 0 de forma assíncrona deveremos ter SET=0 e RESET=1.3 Flip Flop Tipo D (Data FF)Um FF Tipo D tem uma única entrada de dados e a sua finalidade é transferir os dados para a saída quando o pulso de relógio for aplicado. A Figura 5 a seguir mostra um FF tipo D construído a partir de um FF RS. Observe que, como as entradas são complementares não existe a possibilidade de S=R=1.O FF tipo D pode ser construido a partir de um FF tipo JK inserindo uma porta inversora entre as entradas J e KFigura 5 - FF tipo D ( a ) Simbolo ( b ) FF D construido com portas NANDArquivo Multisim Live - Tipo D usando JKCircuito Integrado: 74HC1744. Flip Flop Tipo T (Toggle FF)É obtido a partir de um FF JK Mestre Escravo liigando as entradas J e K. Desta forma teremos somente duas condições para a entrada T (T=0 e T=1). A Figura 6 mostra os símbolos e a TV.Figura 6 - FF tipo T ( a ) símbolo dos FF sensível à borda de subida e descida ( b ) Tabela Verdade5. Experiência: Flip Flop JK5.1. Abra o arquivo ExpDG2_03 FF JK MS com portas e identifique o circuito da Figura 7. Verifique o funcionamento para todas as combinações de entradas da Tabela Verdade da Figura 4.Figura 7 - FF JK mestre escravo com portas logicasArquivo Multisim FF JK com Portas5.2. Abra o arquivo ExpDG2_04 FF JK em CI 7476 (Multisim 14) e identifique o circuito da Figura 8. Execute uma simulação verificando a tabela verdade do FF JK integrado.( a ) ( b )5.3 Abra o arquivo ExpDG2 FF JK Sensivel descida do clock (Multisim Live) e identifique o circuito da Figura 9,. Execute uma simulação Interactive verificando a tabela verdade do FF JK (use a mesma do item anterior).. Figura 9 - FF JK sensivel ao bordo de descidaArquivo Multisim Live5.4 Abra o arquivo ExpDG2 FF JK Sensivel subida do clock (Multisim Live) e identifique o circuito da Figura 10. Execute uma simulação Interactive verificando a tabela verdade do FF JK (use a mesma do item anterior).5.4 Escreva as suas conclusões

Figura 9 - FF JK sensivel ao bordo de descidaArquivo Multisim Live5.4 Abra o arquivo ExpDG2 FF JK Sensivel subida do clock (Multisim Live) e identifique o circuito da Figura 10. Execute uma simulação Interactive verificando a tabela verdade do FF JK (use a mesma do item anterior).5.4 Escreva as suas conclusões